We are a part of the Systems Research Group, focusing on designing and building a secure, efficient, and high-scalable end-to-end computer system by adopting emerging hardware devices. Our research projects leverage a wide range of state-of-the-art hardware technologies/devices, such as accelerators (FPGAs, GPUs, ASICs), SmartNICs, Infrastructure Processing Units (IPUs), trusted execution environments (Intel SGX/TDX, ARM TrustZone, AMD Sev), silicon root-of-trust (OpenTitan), targeting modern cloud computing infrastructures, such as cloud-native environments, serverless computing, distributed systems, resource-disaggregated servers, embedded/IoT systems.

NOTE: we’re looking for students who want to write BSc/MSc theses or participate in Guided Research. If you are interested, please send us your application by following our application instructions.

Ongoing Research Projects

Trustworthy Disaggregated Architectures

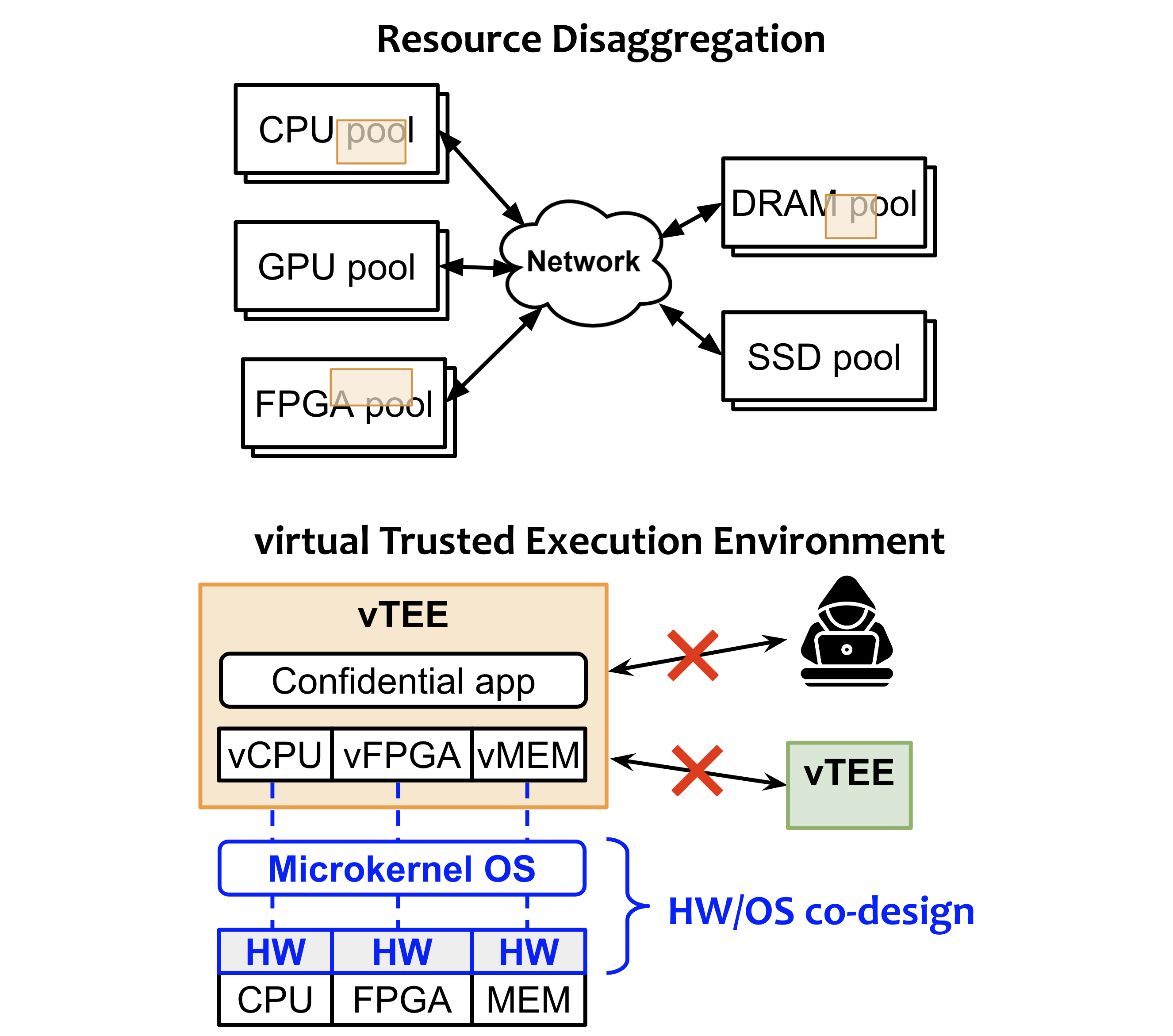

The rising performance demands and increasing heterogeneity in cloud data centers lead to a paradigm shift in the cloud infrastructure, from monolithic servers to a disaggregated architecture. In a multi-tenant cloud, users should be able to leverage trusted computing to protect their applications from untrusted parties. While Trusted Execution Environments (TEEs) are a well-known technique for realizing trusted computing on monolithic servers, we cannot adopt existing TEE technologies to the disaggregated architecture due to their distributed nature and heterogeneity of devices.

This project aims to design and build trusted heterogeneous disaggregated architectures that allow cloud users to construct virtual TEEs (vTEEs): TEE-based, secure, isolated environments assembled with any combination of disaggregated components.

Keywords: Resource disaggregation, Heterogeneous computing, Trusted Execution Environments (TEEs), Intel IPUs, OpenTitan

Cloud-native FPGA Virtualization

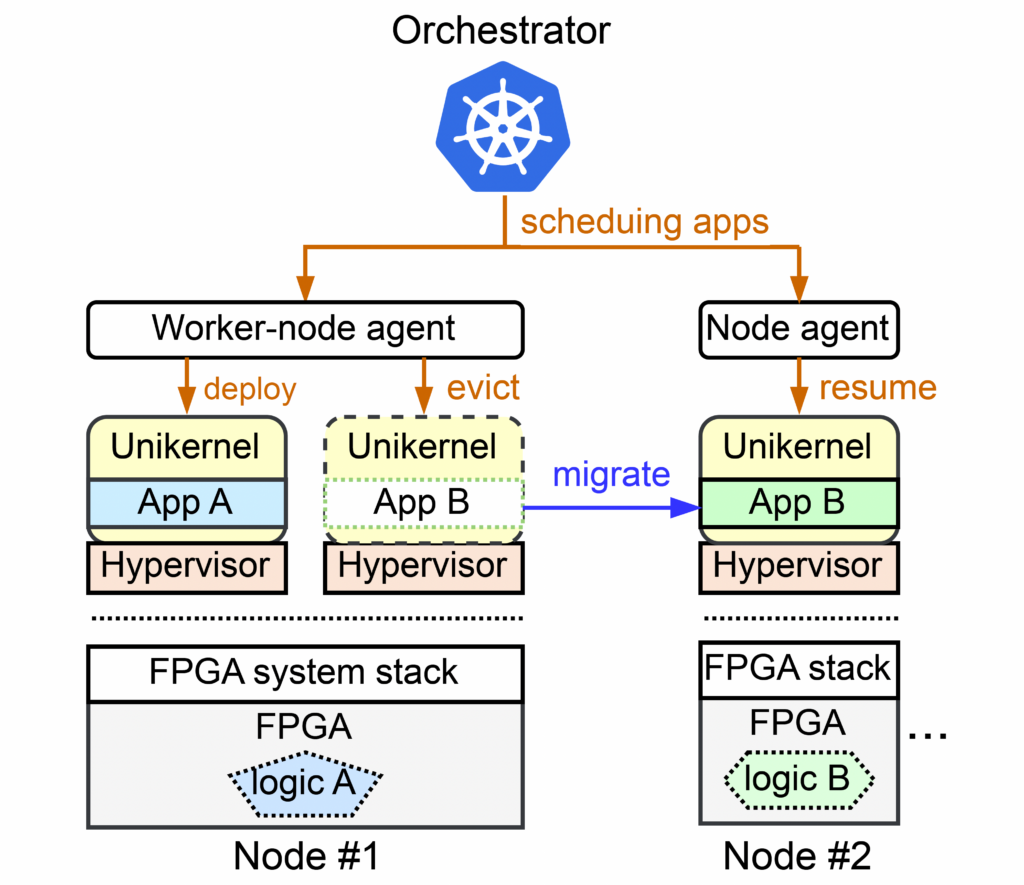

Field Programmable Gate Arrays (FPGAs) are being adopted in cloud-native environments as they are suitable for accelerating modern cloud workloads: machine learning, databases, graph processing, and so on. Despite their advantages, there is currently no distributed FPGA virtualization support in cloud-native environments, which complicates on-demand FPGA management across distributed nodes, such as preemptive scheduling and migration, leading to low resource utilization and high running costs.

This project aims to propose and build a new cloud-native architecture for virtualizing and orchestrating distributed FPGAs in the cloud. Our system leverages a lightweight library OS (unikernel) to facilitate virtualizing distributed FPGAs with negligible performance overheads and realizing pre-emptive task scheduling for FPGA resource orchestration.

Keywords: Cloud-native environments, Microservices, FPGAs, Virtualization, Unikernels

FPGA-accelerated Serverless Computing

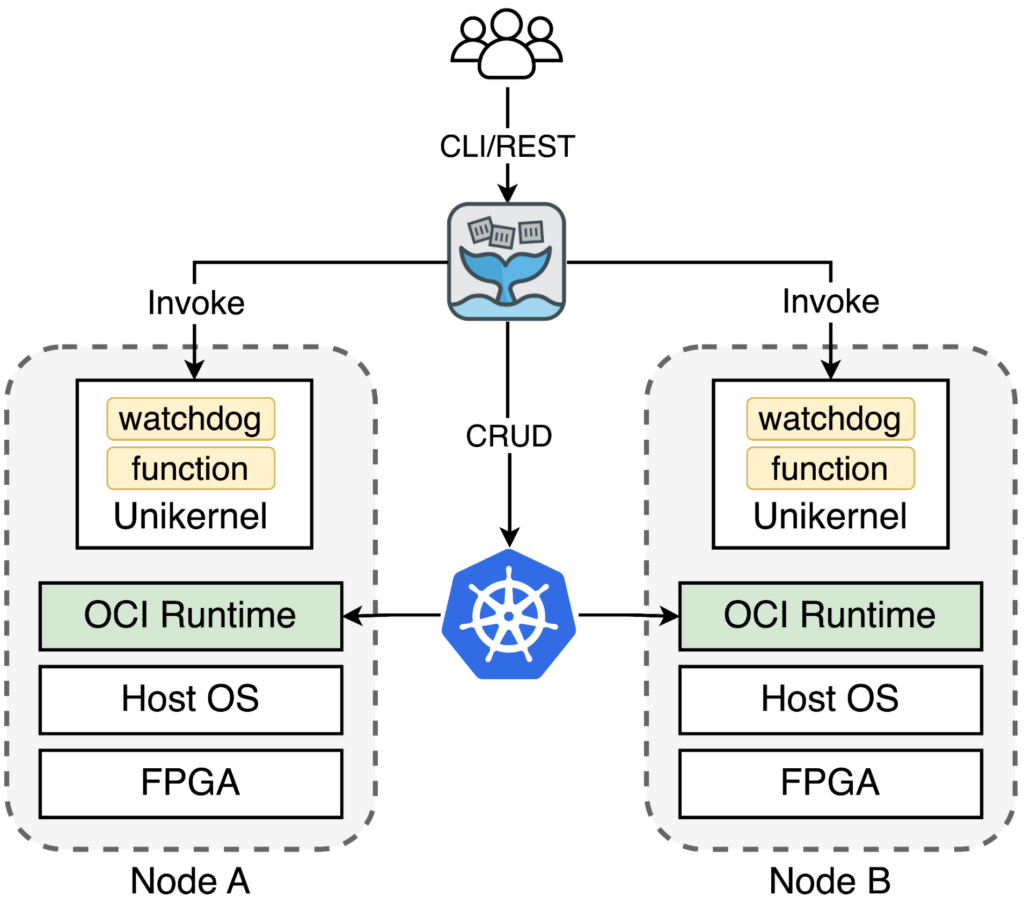

Serverless computing has gained popularity in recent years due to its ease of use, scalability, and cost-effectiveness. At the same time, the increasing complexity of modern workloads has created a pressing need for hardware acceleration in the cloud and serverless computing. FPGAs are suitable for hardware acceleration in serverless environments, offering high flexibility, low latency, and high throughput.

This project aims to build an end-to-end serverless framework that facilitates the use of FPGAs in serverless computing architectures. Users can simply deploy or use FPGA functions without worrying about FPGA device management. Our system handles the execution of FPGA functions, focusing on resource consolidation, isolation, high throughput, and low latency.

Keywords: Serverless computing, FPGAs, Hardware acceleration, Kubernetes

I/O Acceleration Framework for FPGA-based Smart Devices

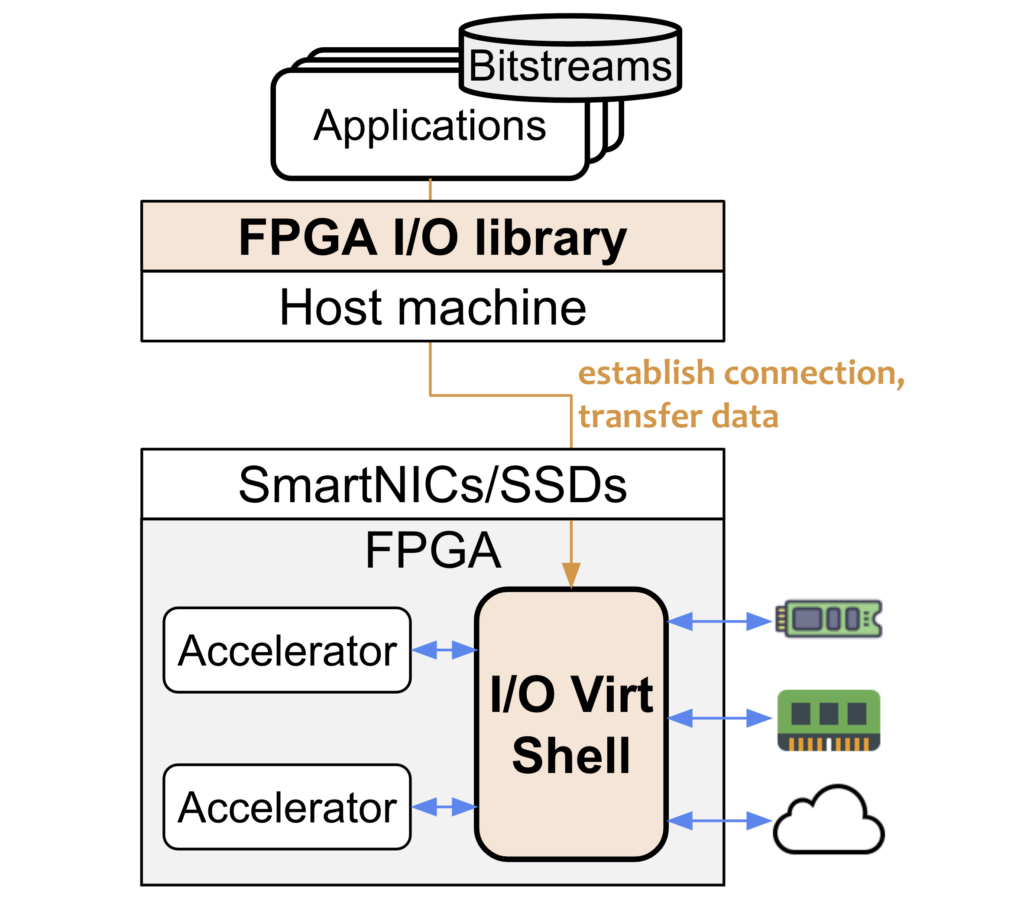

Modern cloud systems have adopted a variety of FPGA-accelerated I/O devices, such as SmartNICs and computational storage, while they face programmability and portability challenges. Existing FPGA frameworks either directly expose device-specific I/O interfaces to user logic or offer virtualized I/Os limited to a single device type. The lack of I/O abstraction imposes high engineering costs, less design portability, and even unexpected throughput degradation.

This project aims to build an FPGA-based I/O acceleration framework that brings better programmability and design portability. The framework offers a new FPGA Shell, a set of dedicated hardware modules to abstract FPGA fabrics, that virtualizes input/output ports of user logic and abstract device-dependent I/O specifications from its hardware design. Host applications can easily configure the connectivity between virtualized I/O ports and external I/O devices through simple APIs.

Keywords: FPGAs, SmartNICs, SmartSSDs, Near-data processing, I/O offloading

Publications: USENIX ATC’24 (to appear)

Group Members

Ongoing & Past MSc/BSc theses, GRs, IDPs

You can find reports, theses, and final presentations of finished projects in our research work archive.

| Student | Type | Title | Advisers | End date |

|---|---|---|---|---|

| Martin Lamback | MSc | Utilizing dynamic partial reconfiguration in an FPGA-accelerated FaaS architecture | Charalampos Mainas, Atsushi Koshiba | 2024, Summer (ongoing) |

| Felix Gust | MSc | Prototyping a Secure Controller for Trusted Heterogeneous Disaggregated Architectures | Atsushi Koshiba | 2023, Summer |

| Bruno Scheufler | BSc | Cloud-Native Scheduling for Serverless FPGAs | Charalampos Mainas, Atsushi Koshiba | 2023, Summer |

| Anand Krishna Rallabhandi | MSc | Heterogeneity-Aware Scheduling Algorithms for FPGA Workloads in Cloud Environments | Atsushi Koshiba | 2023, Summer |

| Jiong Liu | BSc | Evaluation of Data-Intensive Accelerated Functions in Computational Storage Devices | Charalampos Mainas, Atsushi Koshiba | 2022, Winter |

| Yuan Luo | GR | A Comprehensive Study of Coyote Memory System | Atsushi Koshiba, Jiyang Chen | 2022, Winter |

| Julian Pritzi | GR | Securing Hardware Communication using Encryption and Attestation | Harshavardhan Unnibhavi | 2022, Winter |

| Zirong Cai | MSc | Frontend Development of Distributed FPGA Management in Serverless Computing | Atsushi Koshiba, Jiyang Chen | 2022, Winter |

| Julian Pritzi | BSc | An in-hardware cycle-accurate benchmarking tool for security-critical operations | Harshavardhan Unnibhavi | 2022, Summer |